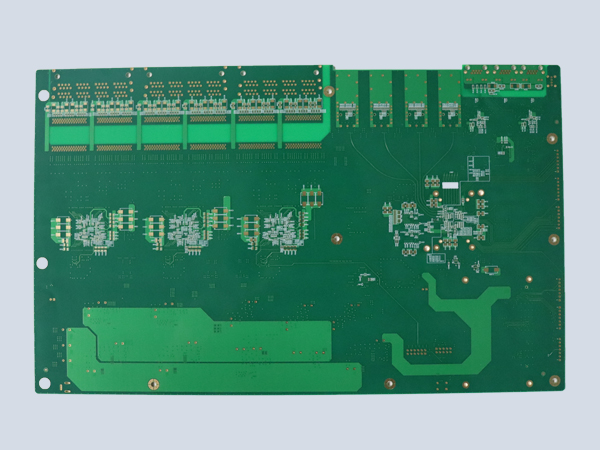

多層PCB基板メーカー多層板24時間の加速サンプリング、HDIブラインド埋設孔72時間の高速サンプリング

15361676619

15361676619

ビア(via)は多層PCBの重要な構成部分の1つであり、ドリルの費用は通常PCB製板の費用の30%から40%を占めている。簡単に言えば、PCB上の各穴はビアと呼ぶことができます。作用的に見ると、ビアは2つの種類に分けることができる:1つは各層間の電気的接続として使用すること、第二に、デバイスの固定または位置決めとして使用されます。プロセスプロセスプロセスから言えば、これらのビアは一般的に3つの種類に分けられ、すなわちブラインドビア、埋め込みビア、スルービアに分けられる。ブラインドホールはプリント配線板の最上部と下層の表面に位置し、表層線路と下層の内層線路との接続のための深さがあり、穴の深さは通常一定の比率(穴径)を超えない。埋め込み穴とは、プリント配線板の内層に位置する接続穴であり、配線板の表面には伸びない。上記の2種類の穴はいずれも配線板の内層に位置し、積層前にスルーホール成形技術を利用して完成し、スルーホール形成過程中にいくつかの内層を重ねて完成する可能性がある。3つ目は、配線板全体を貫通する貫通孔と呼ばれ、内部相互接続や部品としての取り付け位置決め孔を実現するために使用されます。スルーホールはプロセス上より容易に実現でき、コストが低いため、ほとんどのプリント基板は他の2種類のスルーホールを使用せずに使用されています。以下に述べるオーバーホールは、特に説明がないものはすべてスルーホールとして考慮される。設計の観点から見ると、1つのビアは主に2つの部分から構成されており、1つは中間のドリルホール(drill hole)であり、2つはドリルホールの周囲のパッド領域である。この2つの部分のサイズは、穴を通る大きさを決定します。高速、高密度のPCB設計の場合、設計者は常にビアが小さいほど良いことを望んでおり、このテンプレートにはより多くの配線空間を残すことができ、また、ビアが小さいほど、それ自体の寄生容量も小さくなり、高速回路に適していることが明らかになった。しかし、穴のサイズの減少は同時にコストの増加をもたらし、しかも穴を通過するサイズは無制限に減少することはできなく、それは穴を掘る(drill)と電気めっき(plating)などの技術の制限を受けている:穴が小さいほど、穴を掘るのにかかる時間が長くなり、中心位置からもずれやすくなる、また、穴の深さがドリル直径の6倍を超えると、穴壁が銅めっきを均一にすることが保証されない。例えば、通常の6層PCB板の厚さ(貫通孔の深さ)が50ミルであれば、一般的な条件下でPCBメーカーが提供できるドリル直径は8ミルにしかならない。レーザー穴あけ技術の発展に伴い、穴あけのサイズもますます小さくなることができ、一般的に直径が6 Mils以下のビアは、マイクロホールと呼ばれています。HDI(高密度相互接続構造)設計では微孔によく使用され、微孔技術は過孔が直接パッド(Via-in-pad)に打ち付けることを可能にし、これは回路性能を大幅に向上させ、配線空間を節約した。

ビアは伝送線上でインピーダンスの不連続なブレークポイントとして表現され、信号の反射を引き起こす。一般的なビアの等価インピーダンスは伝送路より12%程度低く、例えば50オームの伝送路はビアを通過するとインピーダンスが6オーム減少する(具体的にはビアのサイズ、板厚にも関係があり、減少ではない)。しかし、インピーダンスが不連続であることによるオーバーホールの反射は実際には微々たるものであり、その反射係数は:(44-50)/(44+50)=0.06にすぎず、オーバーホールによる問題は寄生容量とインダクタンスの影響に集中している。二、ビアの寄生容量とインダクタンスビア自体に寄生の浮遊容量が存在し、ビアの舗装層上のソルダーレジスト領域の直径がD 2で、ビアパッドの直径がD 1で、PCB板の厚さがTで、板基材の誘電率がεであれば、ビアの寄生容量の大きさはC=1.41εTD 1/(D 2-D 1)ビアの寄生容量が回路に与える主な影響は信号の上昇時間を延長し、回路の速度を低下させることであることが知られている。例えば、厚さ50 MilのPCB板の1枚に対して、使用されているポーラスパッドの直径が20 Mil(ドリル直径が10 Mils)、ソルダーレジスト領域の直径が40 Milであれば、上の式によりポーラスの寄生容量をほぼ計算することができます:C=1.41 x 4.4 x 0.050 x 0.020/(0.040-0.020)=0.31 pFこの部分の容量による上昇時間変化量は、T 10-90=2.2 C(Z 0/2)=2.2 x 0.31 x(50/2)=17.05 psこれらの数値から分かるように、単一ポーラスの寄生容量による上昇遅延緩慢化の効果は明らかではありませんが、走査線に何度も穴を使用して層間の切り替えを行うと、複数の穴が使用されるので、設計には慎重に考慮しなければなりません。実際の設計では、ビアと銅舗装領域の距離(Anti−pad)を大きくするか、パッドの直径を小さくすることで寄生容量を小さくすることができる。過孔に寄生容量が存在すると同時に寄生インダクタンスも存在し、高速デジタル回路の設計において、過孔の寄生インダクタンスによる危害は寄生容量の影響より大きいことが多い。その寄生直列インダクタンスはバイパス容量の寄与を弱め、電源システム全体のフィルタリング効果を弱める。L=5.08 h[ln(4 h/d)+1]で、Lはビアのインダクタンス、hはビアの長さ、dは中心ドリルの直径を意味するビア近似の寄生インダクタンスを簡単に計算するには、次の経験式を使用します。式から分かるように、ビアの直径はインダクタンスに与える影響が小さく、インダクタンスに与える影響はビアの長さである。上記の例を用いて、ビアのインダクタンスを計算することができる:L=5.08 x 0.050[ln(4 x 0.050/0.010)+1]=1.015 nH信号の立ち上がり時間が1 nsであれば、その等価インピーダンスの大きさは:XL=πL/T 10-90=3.19Ωである。このようなインピーダンスは高周波電流の通過ではもはや無視できないので、特に注意して、バイパス容量は電源層と地層を接続する際に2つのビアを通過する必要があり、そうするとビアの寄生インダクタンスは倍増する。三、どのようにビアを使用してビア寄生特性の分析を通じて、高速PCB設計において、簡単に見えるビアは往々にして回路の設計に大きなマイナス効果をもたらすことが明らかになった。オーバーホールの寄生効果による悪影響を低減するために、設計においてできるだけできる:1.コストと信号品質の両面から考慮して、合理的なサイズのオーバーホールサイズを選択する。必要に応じて、電源やアース線のビアのような異なるサイズのビアを使用することを考慮することができます。インピーダンスを小さくするために大きなサイズを使用することができますが、信号の引き廻しには小さなビアを使用することができます。もちろん、ビアサイズが小さくなるにつれて、その分のコストも増加します。2.上述の2つの公式は、薄いPCBボードを使用することで、ビアの2つの寄生パラメータを低減するのに有利であることを得ることができる。3.PCBボード上の信号の引き廻しはできるだけ層を変えない、つまりできるだけ不必要な穴を使わないようにする。4.電源とアースのピンは近くに穴を開け、穴とピンの間のリード線は短いほど良い。等価インダクタンスを低減するために、複数のビアを並列に打つことが考えられる。5.信号変換層のビア近傍に接地されたビアを配置し、信号に近いループを提供する。PCBボードに余分な接地ビアを置くこともできます。